http://archive.org/details/graphics8graphic371cart

Graphics 8 Graphics Hardware - 1469 Gear

by

C. E. Carter R. Hostovsky H. Levin

- H. Lopeman

- R. Miller

THE WARRY IN THE

December 1969

;N 371

.2

DERARTMENT OF COMPUTER SCIENCE UNIVERSITY OF ILLINOIS AT URBANA-CHAMPAIGN · URBANA, ILLINOIS

universitiet materies FEB 2.5 1970

FEB 2 0 1870

Report No. 371

Graphics 8 Graphics Hardware - 1469 Gear\*

by

- C. E. Carter R. Hostovsky H. Levin H. Lopeman

- R. Miller

December 1969

Department of Computer Science University of Illinois Urbana, Illinois 61801

4

\* Supported in part by grant U. S. AEC AT(11-1)1469.

1.07

. 110

# Graphics 8

10.84 1510 871-392

2 2

Graphics Hardware - 1469 Gear

## CONTENTS

| Introduction |                                                                                                                                                                                         |                                              |  |  |  |  |

|--------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------|--|--|--|--|

| Basic Sys    | stem                                                                                                                                                                                    | 3                                            |  |  |  |  |

| 3.<br>4.     | PDP-8<br>ASR 33<br>Dectape<br>PBD-338<br>Interval Timer                                                                                                                                 | 4<br>15<br>19<br>22<br>31                    |  |  |  |  |

| Operating    | g Additions                                                                                                                                                                             | 32                                           |  |  |  |  |

|              | PDP-8 to 630 Interface<br>Data Disc<br>Data Tablet (Sylvania)<br>Music Generator<br>Push Button Bootstrap<br>Illiac III Interface<br>2701 Parallel Data Adapter<br>Microswitch Keyboard | 33<br>35<br>45<br>51<br>52<br>54<br>55<br>58 |  |  |  |  |

| Proposed     | Additions                                                                                                                                                                               | 60                                           |  |  |  |  |

|              | Inktronic Printer<br>Display Processing Unit                                                                                                                                            | 61<br>71                                     |  |  |  |  |

| Appendix A   |                                                                                                                                                                                         |                                              |  |  |  |  |

| 1.<br>2.     | Alphabetic IOT List<br>Sequential IOT List                                                                                                                                              | 75<br>79                                     |  |  |  |  |

#### Graphics 8

## Introduction

This report was written for two reasons. The first was to serve as a reference manual for the 1469 group in their everyday graphics work. The second was to serve as an applications manual for use by those University people who make use of the graphics facility.

The report is divided into three parts: basic system, operating additions, and proposed additions. The basic system made up of a 16K-PDP-8 with interval timer, an ASR33 Teletype, 2 ea Dectapes, and a PDB-338 was installed and checked-out in June of 1967. The operating additions have been made over the past two years. The proposed additions are being worked-on for purposes of making the total facility better for user applications.

The items that make up the individual parts are described in this report and/or reference is made to another report for a more detailed description.

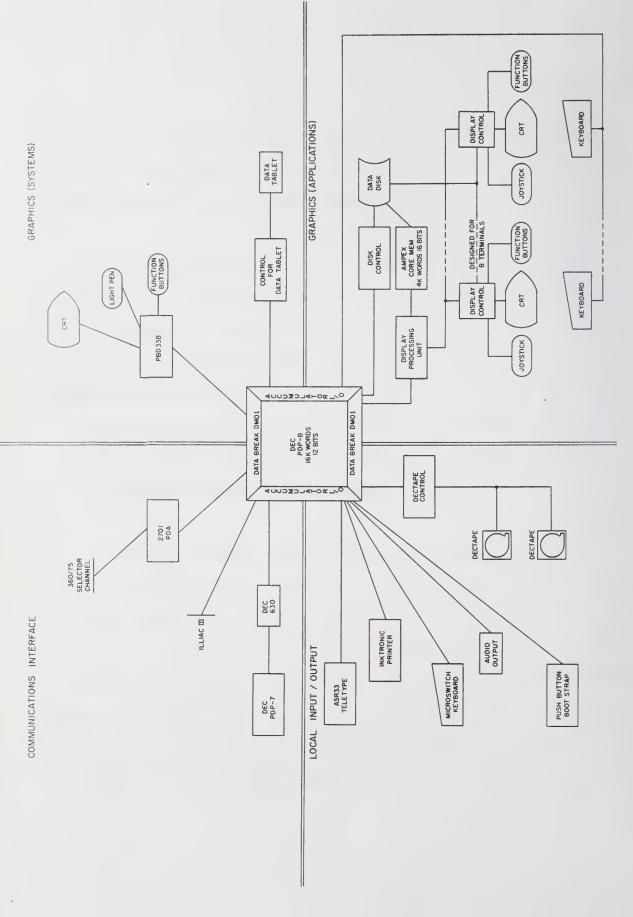

Figure 1 is a configuration drawing of the Graphics 8 hardware. The four quadrants contain devices, controllers or interfaces corresponding to the title of the quadrant. The three communication interfaces have been particularly useful in enhansing the PDP-8 capabilities for graphics developments and user applications. The Graphics (system) is the present basic system tools for graphic work on the PDP-8. The Graphics (applications) is the developmental project for expanding the user facilities of the PDP-8. The local  $I/\emptyset$  contains the various low-speed devices accessable to the user at the PDP-8.

0

figure l

The graphics 8 was ordered as a stand-alone graphics system with the PDP-8 processor, ASR33 teletype, 338 programmed buffered display, dectapes, and interval timer. This section of the report is made-up of short descriptions of each of these five pieces of the basic system.

## PDP-8 INTRODUCTION

The Digital Equipment Corporation Programmed Data Processor-8 (PDP-8) is designed for use as a small-scale general-purpose computer, an independent information handling facility in a large computer system, or as the control element in a complex processing system. The PDP-8 is a one-address, fixed word length, parallel computer using 12 bit, two's complement arithmetic. Cycle time of the 16K word random-address magnetic-core memory is 1.5 microseconds. Standard features of the system include indirect addressing and facilities for instruction skipping and program interruption as functions of input-output device conditions.

Flexible, high-capacity, input-output capabilities of the computer allow it to operate a variety of peripheral equipment. In addition to standard Teletype and performatted tape equipment, the system is capable of operating in conjunction with a number of optional devices such as highspeed perforated tape readers and punches, card equipment, a line printer, analog-to-digital converters, cathode-ray-tube displays, magnetic drum systems, and magnetic-tape equipment. Equipment of special design is easily adapted for connection into the PDP-8 system.

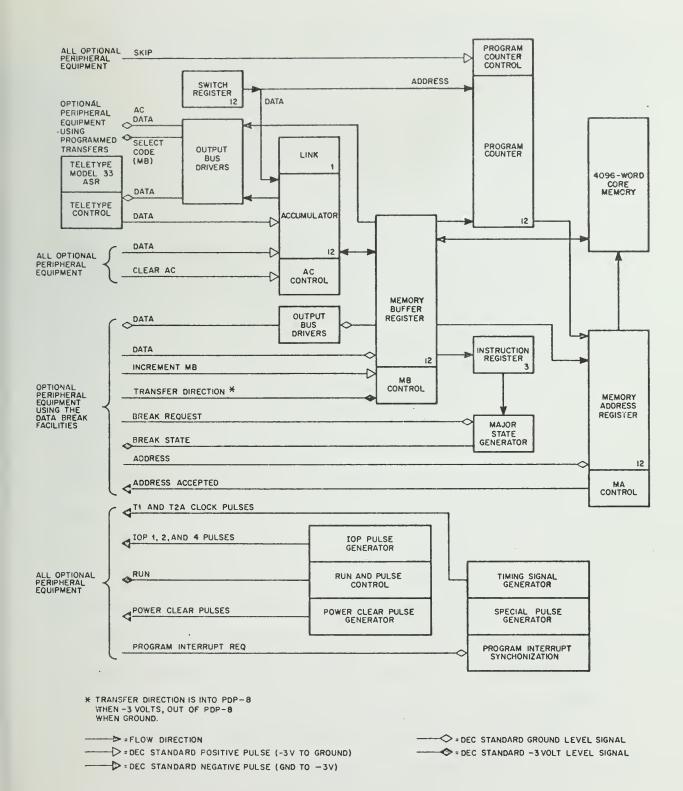

## COMPUTER ORGANIZATION

The PDP-8 system is organized into a processor, core memory, and input/output equipment and facilities. All arithmetic, logic, and system control operations of the standard PDP-8 are performed by the processor. Permanent (longer than one instruction time) local information storage and retrieval operations are performed by the core memory. The memory is continuously cycling and automatically performing a read and write operation during each computer cycle. Input and output address and data buffering

Fig. 2 PDP-8 Block Diagram

for the core memory is performed by registers of the processor, and operation of the memory is under control of timing signals produced by the processor.

Interface circuits for the processor allow bussed connections to a variety of peripheral equipment. Each input/output device is responsible for detecting its own select code and for providing any necessary input or output gating. Individually programmed data transfers between the processor and peripheral equipment take place through the processor accumulator. Data transfers can be initiated by peripheral equipment rather than by the program, by means of the data break facilities. Standard features of the PDP-8 also allow peripheral equipment to perform certain control functions such as instruction skipping and a transfer of program control initiated by a program interrupt.

#### MAJOR REGISTERS

To store, retrieve, control, and modify information and to perform the required logical, arithmetic, and data processing operations, the core memory and the processor employ the logic components shown in Figure 2 and described in the following paragraphs.

## Accumulator (AC)

Arithmetic and logic operations are performed in this 12-bit register. Under program control the AC can be cleared or complemented, its content can be rotated right or left with the link. The content of the memory buffer register can be added to the content of the AC and the result left in the AC. The content of both of these registers may be combined by the logical operation AND, the result remaining in the AC. The memory buffer register and the AC also have gates which allow them to be used together as the shift register and buffer register of a successive approximation

analog-to-digital converter. The inclusive OR may be performed between the AC and the switch register on the operator console and the result left in the AC.

The accumulator also serves as an input-output register. All programmed information transfers between core memory and an external device pass through the accumulator.

## Link (L)

This one-bit register is used to extend the arithmetic facilities of the accumulator. It is used as the carry register for two's complement arithmetic. Overflow into the L from the AC can be checked by the program to greatly simplify and speed up single and multiple precision arithmetic routines. Under program control the link can be cleared and complemented, and it can be rotated as part of the accumulator.

## Program Counter (PC)

The program sequence, that is the order in which instructions are performed, is determined by the PC. This 12-bit register contains the address of the core memory location from which the next instruction will be taken. Information enters the PC from the core memory, via the memorybuffer register, and from the switch register on the operator console. Information in the PC is transferred into the memory address register to determine the core memory address from which each instruction is taken. Incrementation of the content of the PC establishes the successive core memory locations of the program and provides skipping of an instruction based upon a programmed test of information or conditions.

## Memory Address Register (MA)

The address in core memory which is currently selected for reading

or writing is contained in this 12-bit register. Data can be set into it from the memory buffer register, from the program counter, or from an I/O device using the data break facilities.

## Switch Register (SR)

Information can be manually set into the switch register for transfer into the PC as an address by means of the LOAD ADDRESS key, or into the AC as data to be stored in core memory by means of the DEPOSIT key.

### Core Memory

The core memory provides storage for instructions to be performed and information to be processed or distributed. This random address magnetic core memory holds 16K 12-bit words. Memory location  $0_8$  is used to store the content of the PC following a program interrupt, and location  $1_8$  is used to store the first instruction to be executed following a program interrupt. (When a program interrupt occurs, the content of the PC is stored in location  $0_8$  and program control is transferred to location 1 automatically.) Locations  $10_8$  through  $17_8$  are used for auto-indexing. All other locations can be used to store instructions or data.

Core memory contains numerous circuits such as read-write switches, address decoders, inhibit drivers, and sense amplifiers. These circuits perform the electrical conversions necessary to transfer information into or out of the core array and perform no arithmetic or logic operations upon the data.

## Memory Buffer Register (MB)

All information transfers between the processor registers and the core memory are temporarily held in the MB. Information can be transferred into the MB from the accumulator or memory address register. The MB can be cleared, incremented by one or two, or shifted right. Information can

be set into the MB from an external device during a data break or from core memory, via the sense amplifiers. Information is read from a memory location in 0.8 microsecond and rewritten in the same location in another 0.8 microsecond of one 1.6 microsecond memory cycle.

## Instruction Register (IR)

This 3-bit register contains the operation code of the instruction currently being performed by the machine. The three most significant bits of the current instruction are loaded into the IR from the memory buffer register during a Fetch cycle. The content of the IR is decoded to produce the eight basic instructions, and affect the cycles and states entered at each step in the program.

## Major State Generator

One or more major control states are entered to determine and execute an instruction. The major state generator determines the machine state during each computer cycle. The major states are Fetch, Defer, Execute, and Break. Each state is produced as a function of the current instruction and the current state, except for the Break state which is entered upon receipt of the Break Request signal supplied by peripheral equipment. Fetch

During this state an instruction is read into the MB from core memory at the address specified by the content of the PC. The instruction is restored in core memory and retained in the MB. The operation code of the instruction is transferred into the IR to cause enactment, and the content of the PC is incremented by one.

If a multiple-cycle instruction is fetched, the following major state will be either Defer or Execute. If a one-cycle instruction is fetched, the operations specified are performed during the last part of the Fetch cycle and the next state will be another Fetch.

## <u>Defer</u>

When a l is present in bit 3 of a memory reference instruction, the Defer state is entered to obtain the full 12-bit address of the operand from the address in the current page or page 0 specified by bits 4 through ll of the instruction. The process of address deferring is called indirect addressing because access to the operand is addressed indirectly, or deferred, to another memory location.

## Execute

This state is entered for all memory reference instructions except jump. During an AND, two's complement add, or increment and skip if zero instruction the content of the core memory location specified by the address portion of the instruction is read into the MB and the operation specified by bits 0 through 2 of the instruction is performed. During a deposit and clear accumulator instruction the content of the AC is transferred into the MB and is stored in core memory at the address specified in the instruction. During a jump to subroutine instruction this state occurs to write the content of the PC into the core memory address designated by the instruction and to transfer this address into the PC to change control.

## Break

When this state is established, the sequence of instructions is broken for a data break. The break occurs at the completion of the current instruction. The data break allows information to be transferred between core memory and an external device, via the MB. When this transfer has been completed, the program sequence is resumed from the point of the break.

## Output Bus Drivers

Output signals from the computer processor are power amplified by output bus driver modules of the standard PDP-8; allowing these signals to drive a heavy circuit load.

#### Functional Summary

Operation of the computer is accomplished on a limited scale by keys on the operator console. Operation in this manner is limited to address and data storage by means of the switch register, core memory data examination, the normal start/stop/continue control, and the single step or single instruction operation that allows a program to be monitored visually as a maintenance operation. Most of these manually initiated operations are performed by executing an instruction in the same manner as by automatic programming, except that the gating is performed by special pulses rather than by the normal clock pulses. In automatic operation, instructions stored in core memory are loaded into the memory buffer register and executed during one or more computer cycles. Each instruction determines the major control states that must be entered for its execution. Each control state lasts for one 1.5-microsecond computer cycle and is divided into distinct time states which can be used to perform sequential logical operations. Performance of any function of the computer is controlled by gating of a specific instruction during a specific major control state and a specific time state.

#### TIMING AND CONTROL ELEMENTS

Figure 2 shows the timing and control elements described in the succeeding paragraphs and indicates their relationship to the major registers. These elements can be grouped categorically into timing generators, register controls, and program controls.

## Timing Generators

Timing pulses used to determine the computer cycle time and used to initiate sequential time-synchronized gating operations are produced

by the timing signal generator. Timing pulses used during operations resulting from the use of the keys and switches on the operator console are produced by the special pulse generator. Pulses that reset registers and control circuits during power turn on and turn off operations are produced by the power clear pulse generator. Several of these pulses are available to peripheral devices using programmed or data break information transfers.

#### Register Controls

Operation of the AC, MA, MB, and PC is controlled by an associated logic circuit. These circuits, in turn, transmit and receive control signals to and from I/O equipment. Programmed data transfer equipment can supply a pulse to the AC control to clear the AC prior to a data input and can supply a pulse to cause the content of the PC to be incremented, thus initiating an instruction skip. Equipment using the data break facility passes signals with the MA control and MB control to determine the direction and timing of data transfers in this mode.

## Program Controls

Circuits are also included in the PDP-8 that produce the I/O pulses which initiate operations involved in input/output transfers, determine the advance of the computer program, and allow peripheral equipment to cause a program interrupt of the main computer program to transfer program control to a subroutine which performs some service for the I/O device.

### INTERFACE

The input/output portion of the PDP-8 is very flexible and interfaces readily with special equipment, especially in real time data processing and control environment.

The PDP-8 utilizes a "bus" I/O system rather than the more conventional "radial" system. The "bus" system allows a single set of data and control

lines to communicate with all I/O devices. The bus simply goes from one device to the next. No additional connections to the computer are required.

External devices receive two types of information from the computer: data and control signals. Computer output data is present as static levels on 12 lines. These levels represent a 12-bit word to be transmitted in parallel to a device. Data signals are received at all devices but are sampled only by the appropriate one in response to a control signal. Control signals are of two types: levels and timing pulses. Six static levels and their complement are supplied by the MB on 12 lines. These lines contain a code representing the device from which action is required. Each device recognizes its own code and performs its function only when this code is present. There are three timing pulses which may be programmed to occur. These IOP pulses are separated in time by one microsecond and are brought to all devices on 3 lines. These pulses are used by a device only when it is selected by the appropriate code on the level lines. They may be used to perform sequential functions in an external register, such as clear and read, or any other function requiring one, two, or three sequential pulses.

Peripheral devices transmit information to the computer on four types of "busses". These are the information bus, the clear AC bus, the skip bus, and the program interrupt bus. The information bus consists of 12 lines normally held at -3 volts by load resistors within the computer. Whenever one of these lines is brought to ground, a binary 1 will be placed in the corresponding accumulator bit. Each device may use the input bus only when it is selected; and thus, these input lines are time shared among all of the connected devices. The skip bus is electrically identical to the information bus. However, when it is driven to ground the next sequential instruction will be skipped. It too can be used only by the device currently

selected and is effectively time shared. The program interrupt bus may be driven to ground at any time by any device whether currently selected or not. When more than one device is connected to the interrupt bus they should also be connected to the skip bus so the program can identify the device requesting program interruption.

The transmission of device slection levels and timing pulses is completely under program control. A single instruction can select any one of 64 devices and transmit up to three IOP timing pulses. Since the timing pulses are individually programmable, one might be used to strobe data into an external device buffer, another to transmit data to the computer, and the third to test a status flip-flop and drive the skip bus to ground if it is in the enabling state.

Data transfers may also be made directly with core memory at a high speed using the data break facility. This is a completely separate I/O system from the one described previously. It is standard equipment in every PDP-8 and is ordinarily used with fast I/O devices such as magnetic drums or tapes. Transfers through the data break facility are interlaced with the program in progress. They are initiated by a request from the peripheral device and not by programmed instruction. Thus, the device may exchange a word with memory whenever it is ready and does not have to wait for the program to issue an instruction. Computation may proceed on an interlaced basis with these transfers.

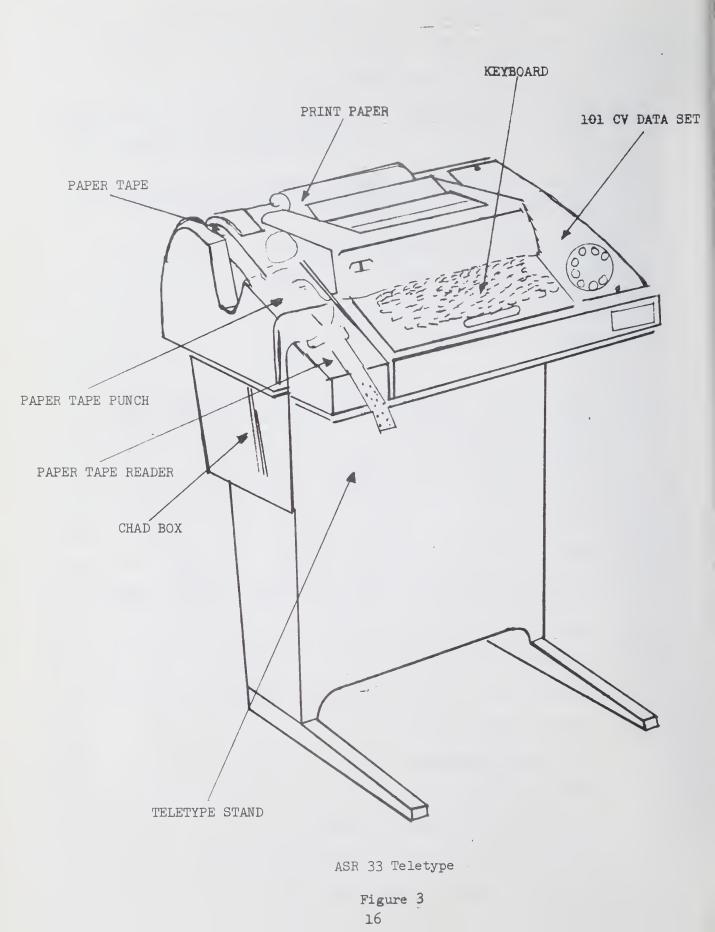

ASR33 (See Figure 3)

Teletype Corporation Model 33TY Standard Duty Automatic Send-Receive Page Printer Set with Tape Perforator and Reader (Private Line Version) has the following features:

Eight-level, 11.0 unit code (1.0 unit start and 2.0 unit stop pulse)

8-1/2" sprocket feed platen with ll" form out and associated reader control

Data communications type wheel arrangement with associated fourrow keyboard layout (American Standard Code for Information Interchange)

115 V AC 60 cycle synchronous motor unit

Gears for 100 wpm operation (110.0 Bauds)

Adjusted for 72 character line

Horizontal spacing 10 characters per inch

Vertical spacing 3 or 6 lines per inch

Selector magnet driver can accept .020 or .060 amperes with proper wiring (strapping)

Generates "even" vertical parity

Two-tone cover: Ivory and Greige

Copyholder

Answer-back drum to be coded by the customer

Function box "online" operation of line feed, carriage return, bell and WRU

Space suppression at end-of-line

Control key (functions)

Shift key (locks out keys without shift case)

Break key and "Here-is" key

Power supply transformer

Convenience outlet

3-way switch (off, online and local)

Wiring provision for optional full duplex operation

Sheet metal stand with Greige color finish

#### Tape Reader Features

3-way operating switch for start, stop and free position "End-of-Tape" mechanism to shut down reader Feed sensing electromagnet is pulsed by the distributor Automatic control contacts for start and "X-ON" code, stop on "X-OFF" code and low paper alarm Power pack assembly with automatic control relay

Parallel wire output to distributor

Operating sequence; reads tape and feeds

Capable of reading fully perforated tape

#### Tape Punch Features

Four operating buttons, "UNLOCK", LOCK "ON", "BACKSPACE", and "RELEASE". (When the lock "ON" button is depressed, the tape punch is locked into the "on" mode and cannot be turned off. When the "UNLOCK" button is depressed, the tape punch will not turn off but will be able to accept an "off" signal and turn off automatically.)

1" Core of tape supply

Fully perforated 8-level code holes and feed holes

"V" shaped tape tearoff

Operating sequence; feed and punch

Removable chad box (designed for attaching to stand)

Automatic control contacts for start on "Tape Aux. On" code, stop of "Tape Aux. Off" code and low paper alarm

## General Information

Interoperates with existing teletypewriters having corresponding features

Fewer options possible compared to Model 35 Heavy-Duty Equipment

Actual and schematic wiring diagrams packaged with set

Set shipped completely assembled less stand and chad box

The above equipment requires a channel capable of handling 110.0 Bauds (bits per second) for operation at 100 wpm.

One copy each of Bulletins 273B and 1184B furnished with each

## Dimensions

Complete set less stand:

| Width  | 22"       |

|--------|-----------|

| Depth  | 18-1/2"   |

| Height | 8-3/8"    |

| Weight | 44 pounds |

Stand: Supports Teletypewriter

| Width  |     |         | 17- | -3/4"  |

|--------|-----|---------|-----|--------|

| Depth  | (at | Top)    | 8'  | t      |

| Depth  | (at | Bottom) | 6-  | -1/2"  |

| Height |     |         | 22- | -1/2"  |

| Weight |     |         | 12  | pounds |

Estimated Service Life

4500 Hours at 100 wpm

Lubrication Intervals (Printer, Tape Punch and Reader)

100 wpm 500 hours or 6 months, whichever is first

Preventive Maintenance and Overhaul

100 wpm 1500 and 3000 hours

NOTE: Hours indicates actual operating time.

### DECTAPE

The Dectapes are connected to the PDP-8 by way of the Data Break Multiplexor feature through a Dectape Control (TCO1). The TCO1 will be described first.

#### Control, Dectape TCO1

The TCOl Dectape Control operates up to eight TU55 Dectape Transports. Binary information is transferred between the tape and the computer in 12-bit computer words approximately every 133-1/3 microseconds. In writing, the control disassembles 12-bit computer words so that they are written at four successive lines on tape. Transfers between the computer and the control always occur in parallel for a 12-bit word. Data transfers use the PDP-8 Block Transfer Control (BTC) (high speed channel) facility of the computer. As the start and end of each block are detected by the Mark track detection circuits, the control raises a Dectape (DTCF) flag which causes a computer program interrupt. The program interrupt is used by the computer program to determine the block number. When it determines that the forthcoming block is the one selected for a data transfer, it selects the read or write control mode. Each time a word is assembled or Dectape is ready to receive a word from the computer, the control raises a data flag. This flag is connected to the computer facility to signify a break request. Therefore, when each 12-bit computer word is assembled, the data flag causes a transfer via the BTC. By using the Mark channel decoding circuits and the BTC in this manner, computation in the main computer program can continue during tape operations.

### Dectape TU55

Dectape is a convenient, low cost in-out data storage facility and updating device.

FIXED POSITION ADDRESSING permits selective updating of tape information as in magnetic disk or drum storage devices. Units as small as a

single computer word may be stored or recorded on tape without disturbing adjacent information. Data blocks are numbered and completely addressable.

AUTOMATIC WORD TRANSFERS use the PDP/8 · Block Transfer Control to allow concurrent information processing and data acquisition during block transfers at 15 kc character rate.

SIMPLE TRANSPORT MECHANISM improves reliability. Dectape's simple drive system requires no capstans, no pressure pad, and no mechanical buffering; therefore tape and head wear is minimal.

POCKET-SIZE REELS are handy to carry, easy to load. Each 3-1/2 inch reel holds up to 3 million bits, the equivalent of 4,000 feet of paper tape, assuming 6-bit words are used.

BI-DIRECTIONAL OPERATION saves time, provides easy access to stored information; reading, writing, and searching may be conducted in either direction.

REDUNDANT, PHASE RECORDING insures transfer reliability, reduces problem of skew in bi-directional operation. Use of phase (rather than amplitude) recording greatly reduces drop-outs due to variations in amplitude.

PRE-RECORDED TIMING AND MARK TRACKS simplify programming. Relieve the programmer of the responsibility of furnishing timing or counting instructions and permit block and word addressability.

PRE-TESTED SUBROUTINES are available for information storage and retrieval, maintenance, and diagnostic tests.

## Dectape Transport Type TU55

The TU55 is a bi-directional magnetic-tape transport consisting of a read/write head for recording and playback of information on five channels of the tape. Connections from the read/write head are made directly to the TCOl external control which contains the read and write amplifiers.

2Q

The logic circuits of the TU55 control tape movement in either direction over the read/write heads. Tape drive motor control is exercised completely through the use of solid state switching circuits to provide reliable operation. These switching circuits contain silicon controlled rectifiers (SCR) which are controlled by normal DEC diode and transistor logic circuits. The function of these circuits is simply to control the torque of the two motors which transport the tape across the head according to the established function of the device, i.e., go, forward, reverse, or stop. In normal tape movement, full torque is applied to the forward or leading motor and a reduced torque is applied to the reverse or trailing motor to keep proper tension on the tape. Since tape motion is bidirectional, each motor serves as either the leading or trailing drive for the tape, depending upon the forward or reverse control status of the TU55. A positive stop is achieved by an electromagnetic brake mounted on each motor shaft. When a stop command is given, the trailing motor brake latches to stop tape motion. Enough torque is then applied to the leading motor to take up slack in the tape.

Tape movement can be controlled by commands originating in the computer and applied to the TU55 through the TCOl Dectape control, or can be controlled by commands generated by manual operation of rocker type switches located on the front panel of the transport. Manual control is used to mount new reels of tape on the TU55, or as a quick maintenance check for proper operation of the control logic in moving the tape.

### PROGRAMMED BUFFERED DISPLAY 338

The Type 338 Programmed Buffered Display is an incremental display system, consisting of a small scale, high speed computer and a display subsystem for control of the CRT. The computer used is the Digital Equipment PDP-8.

#### FUNCTIONAL DESCRIPTION

The 338 display logic can be thought of as a special purpose computer which stores its instructions (display commands) in the memory of the PDP8, and interacts with the computer through a series of instruction interrupts and data transfers. The display is an output device with respect to the computer for the following reasons:

- a. The PDP8 has a series of instructions which start, stop, and load and interrogate the registers of the display.

- b. The PDP8 can modify the data commands which are interpreted by the display because the commands are stored in the PDP8 memory.

The commands are transferred to the display control via the PDP8 single cycle data break system. The display file words are loaded into a table or block of successive memory locations; and the beginning location of this table is loaded into a special register called the display address counter (DAC). The output of the DAC and the break field registers are applied to the inputs of the memory (MA) register forming a 15-bit address which can increment across memory field boundaries. The data break is then

initiated by either the display or the computer, and this address is read into the MA. The computer then goes through a break cycle in which it fetches the word from memory and places it into its memory buffer (MB) register from where it is transferred to the buffer register (DX) in the display. During this time, the display starts its operation and the DAC is incremented by one. The computer program counter (PC) is not incremented during the break cycle. At the end of the break cycle the PDP8 continues its main program until the display requires another data break.

## Display Parameters (Coordinate System)

The display screen which is 9-3/8 inches square, has 10 bits of resolution; in other words there are 1,024 points in the x and y directions or about a million points in all. The x and y position registers are 13 bits long, however, and therefore the screen represents only 1/64 the total addressable area (paper). The paper is broken up into 64 sectors corresponding to the upper 3 bits of x and y, with sector 0 defined as the lower left sector. Only information in sector 0 is intensified so that translation is accomplished by moving the paper in relation to sector 0. The lower left corner is point (0,0), and the coordinates increase to the right and up, and decrease to the left and down. An edge violation occurs when a line is drawn across the boundary of the paper. This is a warning that an overflow condition has just occurred in the x or y position register. A vertical edge flag indicates the y position register went from all 1s to all 0s, or from all 0s to all 1s. The horizontal edge flag indicates overflow in the x register. The overflow can be set to occur after the 10th, 11th, 12th or 13th bit in x and y. The virtual size can therefore be changed under program control.

Scale

The scale setting determines the number of positions each succeeding spot is moved before it is intensified. It affects both the size and appearance of lines or symbols drawn in the vector, vector continue, short vector, increment, or character modes. At scale setting  $ll_2$ , each point can be clearly distinguished. At scale setting  $00_2$ , lines and symbols appear to be continuous. The point spacing is illustrated in the following table.

| Scale | Point Spacing |   |   |   |   |   |   |   |   | Intensify |       |

|-------|---------------|---|---|---|---|---|---|---|---|-----------|-------|

| 002   | •             | • | • | • | ٠ | • | • | ٠ | • | •         | Every |

| 012   | •             | Ö | • | 0 | • | 0 | • | 0 | ٠ | 0         | 2nd   |

| 102   | •             | 0 | 0 | 0 | • | 0 | 0 | 0 | 0 | 0         | 4th . |

| 112   | •             | 0 | 0 | 0 | 0 | 0 | 0 | 0 | • | 0         | 8th   |

#### Intensity

There are eight intensity levels available on the display, ranging from  $000_2$ , which is barely visible, to  $111_2$ , which is very bright. Note that scale and intensity settings are interrelated. For example, if characters are drawn (with the character generator) at the lowest scale setting, and too high an intensity is used, they will be badly blurred. On the other hand, if many characters are to be displayed simultaneously or if the light pen is to be used, it is best to use as high an intensity level as possible.

#### State

The display logic is broken into two states, data state and control state. Control state commands are interpreted as instructions to the display logic to change parameters, jump, skip, etc. The data state commands are instructions to move the beam via the x and y position registers. When the display is initialized, the commands are accepted in control state until an "enter data state" command is given. The display returns to control state from data state by escaping.

In control state, the first three bits (op code) designate the operation to be performed by the remaining nine bits. Seven of the eight op codes are used:

- 0 Parameter

- 1 Mode

- 2 Jump

- 3 Pop

- 4 Conditional skip 1

- 5 Conditional skip 2

- 6 Miscellaneous (microprogrammed)

- 0 Arithmetic compare 1

- 1 Arithmetic compare 2

- 2 Skip on flags

- 3 Count

- 4-7 Set slaves (optional)

- 7 Sync

Data state words are accepted in one of seven formats according to the contents of the mode register. The data state modes available are: <u>Increment Mode</u> - This mode is used to draw alpha numeric characters or other small symbols, and to draw curves. A half-word instruction that will cause the beam position to be stepped one, two, or three times in one of eight directions. Direction 0 is to the right, direction 1 is up and to the right, etc.

<u>Vector Mode</u> - This mode is used to draw straight line segments. A twoword instruction which causes the beam position to be stepped along a line represented by a 10-bit delta y and a 10-bit delta x, each having a sign bit.

<u>Vector Continue Mode</u> - This mode is used to draw a straight line to the edge of the screen. Similar to Vector mode but causes the vector to be extended until an "edge" is encountered.

<u>Short Vector Mode</u> - This mode is used to draw figures composed of short line segments. A one-word instruction having a 4-bit delta y and a 4-bit delta x, plus sign bits. It is transformed within the display to the same format as Vector mode, and operates in the same manner.

The preceding modes are "incrementing;" that is, they move the beam by counting the x and y position registers. The counting is done at 1.2 microseconds per step on an intensified move; at 0.30 microseconds per step on a nonintensified move.

<u>Point Mode</u> - This mode is used for random point plotting. A two-word instruction which causes new y and/or x coordinates to be set into the y and x position registers.

<u>Graph-Plot Mode</u> - This mode is used to draw curves of mathematical functions. A one-word instruction which causes the y or x position register to be changed; at the same time, the other register is incremented by a count of one, two, four, or eight, depending on the current scale factor. This mode is useful for plotting curves resulting from a series of solutions of an equation.

Point and Graph-Plot modes operate at one of two rates, depending upon the position of the new point with respect to the previous point. The high-order three bits of the ten y and ten x position bits are compared to the corresponding bits in the new data words. If they are the same, the delay for beam-settling time is 6 microseconds; if they differ, a 35 microsecond delay is used.

Character Mode - A half-word instruction, using the Type VC38 Character Generator.

All modes are entered from control state by the "enter data state" command. Each mode, however, has its own way of escaping back to control state. The mode register is cleared by power clear and initialization of display (IOT 165).

### Subroutining

The display has control state commands which will modify the DAC. This enables unconditional display jumps (jump), jump to subroutine (push jump) and the return from subroutines (pop). The new address is specified by 15 bits allowing direct addressing of 32 K of core. The jump and push

jump commands are specified by two consecutive 12-bit words. Push jump stores the return address, mode, intensity, scale, and light pen on a push-down pointer list which resides in the first 4 K of PDP8 core. This information is automatically written into two locations in the format shown below.

|   | reak Fiel | d | Light<br>Pen | Sc | ale |   | Mode |   | In | tensity |    |

|---|-----------|---|--------------|----|-----|---|------|---|----|---------|----|

| 0 | 1         | 2 | 3            | 4  | 5   | 6 | 7    | 8 | 9  | 10      | 11 |

First Word

| Low Order 12-Bits of Memory Address |   |   |  |   |   |   |   |   |   |   |   |    |    |

|-------------------------------------|---|---|--|---|---|---|---|---|---|---|---|----|----|

|                                     | 0 | 1 |  | 2 | 3 | 4 | 5 | 6 | 7 | 8 | 9 | 10 | 11 |

Second Word

The information is placed in the address indicated by the push-down pointer, (PDP) which is a 12-bit register in the display logic. When a push jump is executed, the PDP is incremented twice, adding a new entry to the PDP list. This allows multi-level and recursive subroutines in the display.

The pop command takes the last entry on the PDP list from core and gates it back to the proper registers. The display status, however, can be inhibited from being restored. The PDP is automatically decremented by two, making the PDP list a last in first out stack.

#### Light Pen

The light pen is an input device which generates a signal (flag) that can be sensed and interpreted by the computer. A light pen interruption stops the display, leaving the contents of all display registers intact, and signals the computer that an interruption has occurred. When this happens, the programmer can examine the contents of the display registers to determine the location (on the display) of the point of light that was sensed by the light pen and/or determine the memory location of the data word specifying that point. The light pen detects light in the range 4300 to 5600 angstroms.

### Pushbuttons

The 338 is equipped with a bank of twelve pushbuttons. They are placed six in a row with a clear button to reset that group. The buttons in each group are interlocked, but two buttons in different groups can be pressed simultaneously. Pressing a button complements an associated flip-flop. For reference, the pushbutton is lit when its flip-flop is in the 1 state. The state of the pushbuttons can be sensed both by the display, using the control state skip instructions, and the PDP8, which can read the state of the pushbuttons into the accumulator. The PDP8 and display can also clear and set the pushbuttons. This enables three-way communication between the operator, display logic, and PDP8. The buttons are labeled 0 through 11 and are packaged in a compact, portable box. The box is connected to the display by a 20 foot cable. There is also a special computer interrupt button on the box.

### Flags

There are a number of special conditions that can arise in the display which require the attention of the PDP8 processor. These conditions are indicated by display flags which can interrupt the computer and be sensed by IOT skip instructions. The flags are:

- a. Internal stop

- b. External stop

- c. Edge

- d. Light pen find

- e. Push button hit

- f. Manual interrupt

The flags can be separated into two groups; a-d are flags which stop the display; e-f are flags which do not stop the display. Group 1 flags are cleared in one of three ways: initialization of a display sequence; resuming from the point the display stopped; and a pulse to clear the flag if the display is no longer needed. The basic system was installed with an interval timer. It was changed to synchronize with the line voltage. The orders associated with the timer are:

> 6311 Skip on <u>no</u> timer flag,

> 6312 Clear timer flag, enable timer interrupt,

> 6314 Disable timer interrupt. (H. Levin)

# Operating Additions

Very soon after the Graphics 8 was put into operation it became obvious that it could not stand alone and was in need of a number of hardware improvements. The list began with a slow link to a large 360 installation and carried through a Data Disc for more local storage, a Data Tablet for input, an Audio Output for sound production, a push button bootstrap for convenience, an Illiac III connection for testing applications, a 2701 P.D.A. for more rapid access to 360 and a microswitch keyboard for replacement of the teletype keyboard.

# PDP8 TO 630 INTERFACE

### General Description

The PDP8 to 630 interface is a half duplex, 100 CPS, serial input to the 630 Data Communications unit. The 630 has no knowledge of the port being anything other than a high speed serial device.

The interface consists primarily of:

- 1. An entry to the PDP8 accumulator,

- 2. An entry from the PDP8 accumulator,

- 3. Six IOT instructions to control transfers,

- An entry to the PDP8 skip bus, interrupt bus, and clear ACC bus,

- 5. A DEC 4706 receiver card, and 4707 transmitter card,

- 6. Miscellaneous control logic.

### Instruction Set

IOT 6631 - SKIP ON RECEIVER FLAG

6632 - CLR ACC AND REC FLAG

6634 - GATE REC TO ACC

6641 - CLR INT. ENABLE

6642 - SET INT. ENABLE

6644 - CLR TRANSMITTER FLAG AND INPUT DATA FROM ACC

Due to the half duplex mode of operation an echo is generated in the receiver when data is transmitted. This allows testing of transmitter completion with an IOT 6631.

# Transmitter

Transmitting data to the 630 consists of gating the ACC. contents into the transmitter with an IOT 6644. The interrupt enable

flag must have been set with an IOT 6642 in order to test for transmitter completion. The IOT 6644 also enables the shift clock and starts transmitting data. The receiver is active during transmission and receives the transmitted data as it is going to the 630. When the receiver flag comes on, it has received the complete character. A test of the receiver flag with an IOT 6631 will generate a program skip when the flag is present. A new character may then be transferred from the accumulator to the transmitter.

### Receiving

Receiving data from the 630 consists of clearing the receiver flag and enabling the interrupt. An incoming character will set the receiver flag and generate an interrupt (if allowed). A test of the receiver flag with an IOT 6631 will generate a program skip, indicating a character is present. An IOT 6634 will gate the contents of the receiver into the accumulator.

(R. Miller)

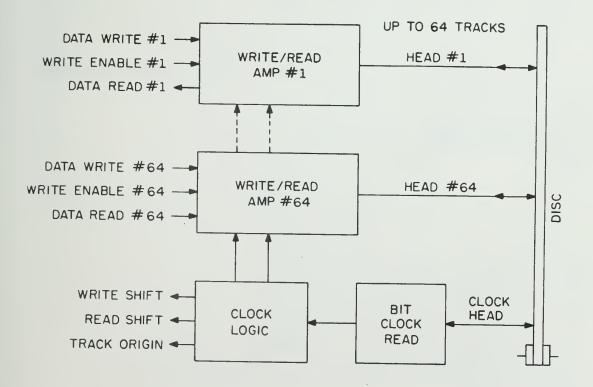

### Data Disk

The following information describes our disk storage system with the exception that:

The 64 heads of electronics will be divided into 32 groups of 2 heads each.

# Summary of Specifications

s,

| Disk Speed                              | 1800 RPM +1.32 - 3%<br>Hysteresis Synchronous Motor                                                |

|-----------------------------------------|----------------------------------------------------------------------------------------------------|

| Data Rate<br>Data Capacity              | 3.0 Mbps per track<br>100,000 bits per track (tracks can<br>be added in increments of 8, up to 64. |

| Input/Output<br>Levels                  | 0 and +5V TTL integrated circuit interface                                                         |

| <br>Environmental                       | Operating temp: 50°F 105°F.; less<br>than 20°F. change per hour.                                   |

|                                         | Non-operating: -20°F +130°F.                                                                       |

|                                         | Operating humidity: 10% - 80% RH without condensation.                                             |

|                                         | Non-operating humidity: to 90% RH without condensation.                                            |

|                                         | Corrosive atmospheres such as those<br>found in steel and chemical plants are<br>not permitted.    |

|                                         | Floor vibration of 0.15 g's max.<br>from 10 to 65 Hz.                                              |

|                                         | The disk package shall not be damaged<br>by 5 g's or less of shock in any axis.                    |

| AC Power                                | 120V <u>+</u> 10%, 60 Hz +0.5 -1.5 Hz single<br>phase 8.2A starting (10 sec.);<br>2.6A running     |

| DC Power<br>Requirements<br>(Per track) | +18V at 125 ma (while writing)<br>+6V at 90 ma)<br>-6V at 40 ma) <u>+</u> 5% regulation            |

| (Power supplied by inter                | nal power supply.)                                                                                 |

| Weight                                  | 86 pounds                                                                                          |

### General Description

### Electrical

The F-series Parallel Digital Disk Memory System has a 12-inch disk which can contain as many as 64 data tracks with 100,000 bits on each track. The disk rotates at 1800 RPM and the bit rate is 3 million bits per second.

The FPD unit is designed for display buffer storage applications. The disk unit uses synchronous clocking from a clock track and is recommended for temporary storage only. Where data is to be stored for an indefinite period, the Data Disk F6 Memory should be employed.

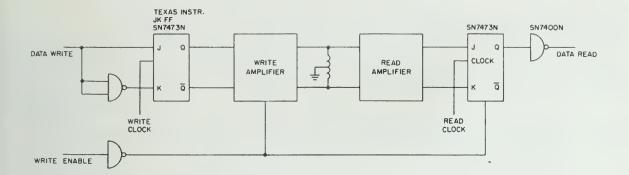

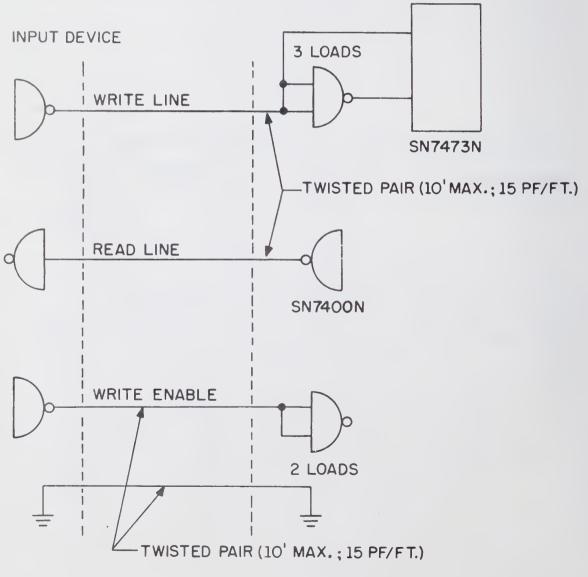

Each track is complete with a read/write head and all electronics to perform the following functions (Figures 4, 5):

Encode data Write data Read data Decode data Re-clock data

Any number of tracks may be written or read in parallel, since each has a clocked flip-flop output.

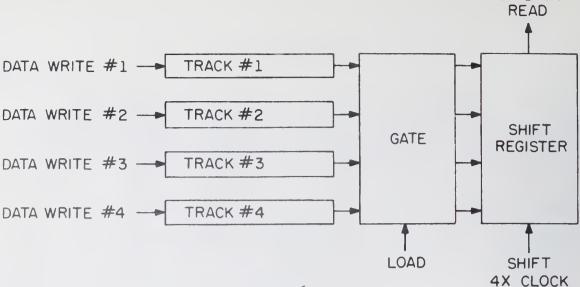

# System Application

The FPD unit is designed so that each track on the disk may feed a separate TV monitor display. A high-speed processor can access each track and update the presentation stored upon any track. Where display rates higher than 3 million bits per second are needed, more than one track can be combined to form the display buffer. For example, data read from four channels may be loaded into a four-bit shift register and with a 4X clock the data can be shifted into the display channel at a 12 million bit rate (Figure 6). Any number of tracks, up to 64, may be combined.

Figure 4

Figure 5

Figure 7

### Input/Output Details

### Input/Output Lines

Each track has three input/output lines that are sent over two twisted pairs of cables, as shown in Figure 7. The FPD unit uses Texas Instrument Series SN7400N and SN7473N TTL integrated circuits.

### Input Connectors

Eight 34-pin connectors are provided, each serving eight heads. The use of 16 heads would require two connectors, etc. All eight connectors (S1 through S8) would be required if 64 heads were used. (See Table 2.) Table 2 also indicates the function served by each pin on each connector, as well as the tracks served by each.

|                                | Table 1                                                                                                                                                                                                                                                                                                    |  |  |  |  |

|--------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Data I                         | nput/Output Lines                                                                                                                                                                                                                                                                                          |  |  |  |  |

| Data Write 1 thru 64:          | An input line that is driven from output<br>of a flip-flop that is clocked by Data<br>Write Shift Clock.                                                                                                                                                                                                   |  |  |  |  |

| <u>Write Enable l thru 64:</u> | The Write Enable line going high will<br>cause the data on the corresponding Data<br>Write line to be written on the track.<br>As long as the Write Enable line is high,<br>writing will continue.                                                                                                         |  |  |  |  |

| <u>Data Read 1 thru 64:</u>    | Each Data Read line is the buffered out-<br>put of a clocked flip-flop. The Data<br>Read is delayed 2 bits times from Data<br>Write and may be shifted into an external<br>register by using the negative edge of<br>Data Read Shift Clocks. During Write the<br>output of the Data Read line is held low. |  |  |  |  |

| Pin<br>No. | Function                                      | Tracks Assigned to Conn.<br>S1 S2 S3 S4 S5 S6 S7 S8 | Pin<br>No. | Function                          | Tracks Assigned to Conn.<br>Sl S2 S3 S4 S5 S6 S7 S8 |

|------------|-----------------------------------------------|-----------------------------------------------------|------------|-----------------------------------|-----------------------------------------------------|

| P P        | *Data Write Track No.<br>Data Read Track No.  | 1 9 17 25 33 41 49 57<br>1 9 17 25 33 41 49 57      | N          | Write Enable Track No.<br>Ground  | 1 9 17 25 33 41 49 57<br>1 9 17 25 33 41 49 57      |

| υA         | *Data Write Track No.<br>Data Read Track No.  | 2 10 18 26 34 42 50 58<br>2 10 18 26 34 42 50 58    | M          | Write Enable Track No.<br>Ground  | 2 10 18 26 34 42 50 58<br>2 10 18 26 34 42 50 58    |

| मि मि      | *Data Write Track No.<br>Data Read Track No.  | 3 11 19 27 35 43 51 59<br>3 11 19 27 35 43 51 59    | Z K        | "Write Enable Track No.<br>Ground | 3 11 19 27 35 43 51 59<br>3 11 19 27 35 43 51 59    |

| н          | *Data Write Track No.<br>Data Read Track No.  | 4 12 20 28 36 44 52 60<br>4 12 20 28 36 44 52 60    | ದ್         | "Write Enable Track No.<br>Ground | 4 12 20 28 36 44 52 60<br>4 12 20 28 36 44 52 60    |

| ΓK         | *Data Write Track No.<br>Data Read Track No.  | 5 13 21 29 37 45 53 61<br>5 13 21 29 37 45 53 61    | טיט        | "Write Enable Track No.<br>Ground | 5 13 21 29 37 45 53 61<br>5 13 21 29 37 45 53 61    |

| M          | *Data Write Track No.<br>*Data Read Track No. | 6 14 22 30 38 46 54 62<br>6 14 22 30 38 46 54 62    | 4H 60      | Write Enable Track No.<br>Ground  | 6 14 22 30 38 46 54 62<br>6 14 22 30 38 46 54 62    |

| 4 H        | *Data Write Track No.<br>*Data Read Track No. | 7 15 23 31 39 47 55 63<br>7 15 23 31 39 47 55 63    | h<br>i     | Write Enable Track No.<br>Ground  | 7 15 23 31 39 47 55 63<br>7 15 23 31 39 47 55 63    |

| ທ E4       | Data Write Track No.<br>*Data Read Track No.  | 8 16 24 32 40 48 56 64<br>8 16 24 32 40 48 56 64    | Ĵ<br>K     | Write Enable Track No.<br>Ground  | 8 16 24 32 40 48 56 64<br>8 16 24 32 40 48 56 64    |

| E          | Unassigned                                    |                                                     | ц          | Unassigned                        |                                                     |

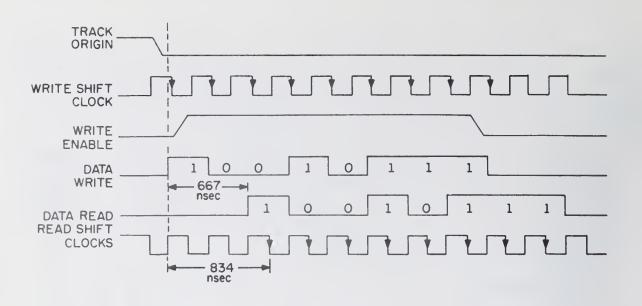

#### Clocks

Five clocks, all derived from one track, are available in the standard FPD system. Two are used internally, and the other three are for use at the interface. The three interface clocks are the Track Origin (once per revolution), Write Shift and Read Shift (Figure 8 and Table 3).

The Write Shift Clocks are used to change the state of the Data Write line and are counted down to indicate angular position of the disc. The Track Origin clock is derived from the six-bit gap in the clock track and is used to indicate the zero degree position of the disc and as a reset for any counters used to identify other angular positions.

### Clock Connector S9

S9 is a 34-pin used by the clock track only. (See Table 4 for pin assignments.)

Table 3

#### Clock Output Lines

Data Write Shift Clock:

A 3-million bit per second clock with 6 clocks missing at Track Origin time.

The negative edge is used for changing state of Data Write lines.

Data Read Shift Clocks:

Inverted Data Write Shift Clocks. The negative edge is used for sampling the Data Read lines. The Data Read is delayed 2 bit times from Data Write.

Data Origin Clock:

A once-per-revolution clock used to reset counters, etc.

Figure 8

Table 4

Pin Assignment 34-Pin Clock Connector S9\*

| Pin<br>No. | Function                                       |   |              |  |  |  |  |  |  |

|------------|------------------------------------------------|---|--------------|--|--|--|--|--|--|

| A          | Write shift clocks                             | ) | Twisted pair |  |  |  |  |  |  |

| B          | Ground                                         | ) |              |  |  |  |  |  |  |

| C          | Read shift clock                               | ) | Twisted      |  |  |  |  |  |  |

| D          | Ground                                         | ) | pair         |  |  |  |  |  |  |

| E          | Track origin clock                             | ) | Twisted      |  |  |  |  |  |  |

| F          | Ground                                         | ) | pair         |  |  |  |  |  |  |

| H<br>J     | Clock data write line<br>Clock write enable li | 1 | Twisted pair |  |  |  |  |  |  |

| *Da1       |                                                |   |              |  |  |  |  |  |  |

#### Operation

#### Write

To write, the first bit of data is placed on the Data Write line and at the correct angular position the Write Enable line is raised and writing begins. Each negative-going transition of the Write Shift clock is used by the external device to transfer another data bit onto the Data Write line. The turn on of the Write Enable should occur at no later than 100 nanoseconds of the negative edge of a Write Shift clock. Write Enable should be turned off at the next positive-going clock transition following the last shift clock. (See timing diagram, Figure 8.)

### Read

During Write the Data Read line is held low but at all other times, any data on the track will be clocked out to the Data Read line. The data may be transferred from the Data Read line to an external device at the negative edge of the Read Shift Clock.

#### GENERAL INFORMATION

### Introduction

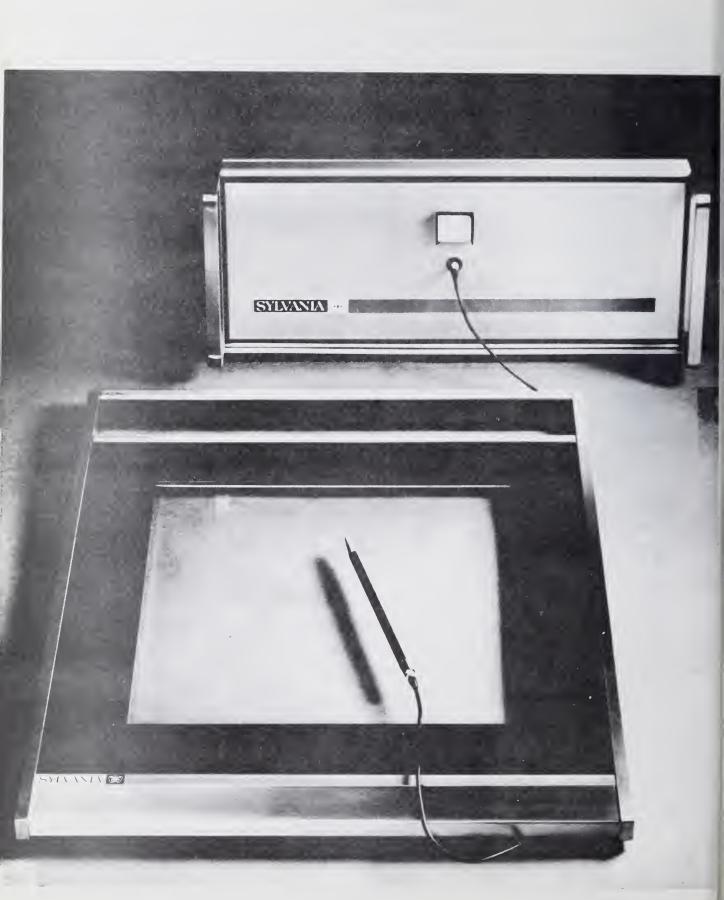

The SYLVANIA DATA TABLET MODEL DT-1 is a coordinate encoder designed to permit graphical communication between man and computer. This solid state system enables the user to enter hand-printed alphanumeric data, curve tracing and modification data, or any other form of handgenerated graphic data into a computer system. The DT-1 is completely contained within three units--a metal rimmed transparent glass writing panel, an electronic pen, and a 1.5 cubic foot electronics package.

### Description

The Sylvania Data Tablet is inherently an analog device in which coordinate information is obtained by phase measurements. Several advantages are forthcoming from this: First, the continuous nature of analog signals allows infinite resolution limited only by system noise. Second, since amplitude stability is not necessary, a capacitance pick up (pen) can be used and dielectric layers may be interposed between it and the active surface. The writing panel of the Sylvania Data Tablet consists of a transparent, continuous conductive film bonded to a heavy glass base plate. A thin glass sheet is laminated to the exposed surface of the film to prevent wear and contamination. A drive network coupled to the electronics package excites the film at discrete points along its circumference in such a manner that a traveling wave (in a mathematical sense) is established parallel to each orthogonal axis. This wave has the property that its phase is a linear function of position as in the relationship:

$$V = K \sin(\omega t - \alpha \chi)$$

The actual tablet signals are more complicated due to the requirement for axis separation. The latter is accomplished by introducting individual frequency translations to the drive signals.

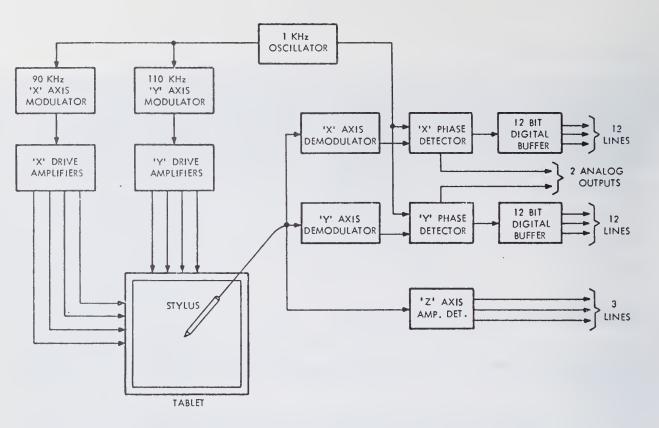

Figure 9 Sylvania Model DT-I Block Diagram

Figure 9 is a block diagram of the Sylvania Data Tablet. A stable 1 KHz sinusoid oscillator generates the primary signal (which will later contain the desired phase shift) used in the system. Balanced modulators operating with 90 KHz and 110 KHz carrier frequencies multiplex the primary signal to different portions of the frequency spectrum as double-sideband suppressed-carrier signals. These are buffered by the 'X' and 'Y' drive amplifiers which in turn drive the conductive film network through a shielded drive cable. An electronic pen (with a high input impedance amplifier built in), capacitively senses the field in the region beneath the pen tip through the glass laminate and any overlayed paper. The voltage is transferred to the electronic package via the attached coaxial cable.

Circuitry within the electronics package separates the pen signals into 'X' and 'Y' channels and extracts the phase information. The desired phase is observed in the envelope waveform of the signals while the axis information is contained in the carrier frequencies. 'X' and 'Y' axis demodulators, which are in fact synchronous detectors keyed by the carrier oscillators, extract the 1 KHz envelopes from the complex pen signals. Phase detectors then compare the demodulator outputs against the 1 KHz primary signal and produce analog and digital voltages proportional to the phase shifts.

An additional circuit measures the amplitude of the pen signals and provides a coarse measure of height ('Z' axis).

### Specifications

SYLVANIA DATA TABLET MODEL DT-1

### ELECTRICAL

| Accuracy         | + 1% of full scale in each coordinate axis                                                                              |

|------------------|-------------------------------------------------------------------------------------------------------------------------|

| Resolution       | $\frac{+}{5}$ .025% of full scale or 12 binary bits at 5 Hz bandwidth                                                   |

| Bandwidth        | 20 Hz supplied                                                                                                          |

| Data rate        | 200 coordinate points per second                                                                                        |

| Digital outputs: |                                                                                                                         |

| 'X' and 'Y' axis | Two 12 bit buffer register outputs<br>availableupdated every 5 milliseconds                                             |

| 'Z' axis         | One bit for each threshold. Output levels<br>are designated 000, 001, 011, 111<br>updated independent of system timing. |

| Data Ready Line  | Set to 'zero' five microsec. before X-Y<br>buffers change and reset to 'one' state<br>five microsec. after change       |

| 'One' state      | +4 volts                                                                                                                |

| 'Zero' state     | +.5 volts                                                                                                               |

| Maximum load     | 600 pf. at 10 milliamps for either state                                                                                |

|      | Analog Outputs:                      |                                                                                                                                                                             |

|------|--------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|      | 'X' and 'Y' axis                     | Two buffered output lines with a dc<br>voltage proportional to position.<br>Range is from -2 volts to +2 volts<br>with zero at the center. Output<br>impedence is 500 ohms. |

|      | 'Z' axis                             | Same as digital except inverted. Output<br>impedance is 850 ohms in high state and<br>20 ohms in the low state.                                                             |

|      | External connectors<br>and controls: |                                                                                                                                                                             |

|      | Front panel                          | Power on-off switch with built-in pilot light.                                                                                                                              |

|      |                                      | Miniature coaxial connector for the electronic pen                                                                                                                          |

|      |                                      | 14 pin auxiliary writing panel connector                                                                                                                                    |

|      | Rear panel                           | 34 pin digital output connector containing<br>the 'one' side of the 'X-Y' buffer<br>registers. Three 'Z' axis bits and the<br>Data Ready Line are also available.           |

|      |                                      | 9 pin analog output connector containing<br>'X' and 'Y' dc outputs and three 'Z'<br>axis bits.                                                                              |

|      |                                      | 14 pin writing panel drive connector                                                                                                                                        |

|      |                                      | Three-prong power connector                                                                                                                                                 |

|      |                                      | Power line fuse3 amps                                                                                                                                                       |

|      |                                      | Three power supply fuses3 amps                                                                                                                                              |

|      | Power source                         | 105 to 125 volts 60 Hz, 150 watts                                                                                                                                           |

|      | Operating temp. range                | +10°C. to +40°C.                                                                                                                                                            |

| MECI | HANICAL                              |                                                                                                                                                                             |

|      | Writing panel dimen-<br>sions        | 15" x 16" x 3/4"                                                                                                                                                            |

|      | Writing aperture                     | 11" x 11"                                                                                                                                                                   |

| Electronic package<br>dimensions | 17" x 18 1/2" x 7"          |

|----------------------------------|-----------------------------|

| Writing panel weight             | Approximately 15 pounds     |

| Electronic package<br>weight     | Approximately 35 pounds     |

| Pen replacement cartridge        | "Papermate" standard refill |

### Operation

The Sylvania Data Tablet Model DT-1 may be used as a table-top unit or a transparent overlay for a computer-controlled cathode ray tube display. For the latter use, the bottom plate must be removed by taking out the eight mounting bolts on the bottom. The writing panel may then be mounted over the face of the CRT and the electronic pen used in a "light pen" fashion. Rear projection techniques may also be employed by placing a translucent diffusing overlay on the writing panel.

The electronic package may be converted from table top to relay rack operation by attaching the included adaptor brackets. The writing panel may be mounted up to ten feet (with appropriate cable) from the electronic package using either the front or rear 14-pin panel connectors. The electronic pen can only be connected at the front panel of the electronic package. Analog outputs are available on a 9-pin jack and digital outputs on a 3<sup>4</sup> pin jack both mounted on the rear panel. A three prong connector and power cord are supplied for connecting 115 volts, 60 Hz to the Model DT-1.

The digital output is a binary parallel format for the 'X' and 'Y' axis. Two 12-bit words are simultaneously stored in buffer registers which are updated 200 times per second by internal timing signals. A Data Ready Line, available at the digital connector, drops to the "zero" state five microseconds before the buffer registers are updated and returns to the "one" state five microseconds following the transfer. Only 100 nanoseconds are required to load the buffer registers which remain quiescent during the

remainder of the five millisecond period. The center of the tablet corresponds to binary <u>100 000 000 000</u>. The left and bottom edges are represented by <u>000 000 000 000</u>; the top and righthand edges by <u>111 111 111 111</u>.

A 'Z' axis (pen height above the writing panel) three-bit word is also available at the digital connector. Each bit corresponds to an adjustable threshold level and is independent of digital timing. As the stylus approaches the writing panel surface from a remote position, the 'Z' representation changes in the following manner: 000 (over 1 inch away), 001, 011, (touching the tablet), and finally 111. The maximum value is reached only when a slight downward pressure is applied to the pen forcing the closure of built-in switch contacts.

The analog outputs are internally buffered and are protected against short circuit. Zero volts corresponds to the center position while the left and bottom edges produce minus two volts dc; the right and top edges produce plus two volts dc. Both analog outputs and three 'Z' axis bits are available on the 9-pin analog connector.

### PDP/8 MUSIC GENERATOR

# Introduction

The PDP/8 music generator is a low cost device that is capable of producing audio tones over a speaker. Its main purpose is to allow a program to audibly signal a user about various conditions, e.g., an illegal command has been entered, an error has occurred, etc.

### Hardware

The music generator consists of:

- 1. An IOT decoder board;

- 2. Two flip-flops resistively coupled to:

- 3. An audio amplifier;

- 4. A loudspeaker.

# Instructions '

The following instructions are used in programming the music generator:

6701 - clear both flip-flops

6702 - complement flip-flop 1

6704 - complement flip-flop 2

### PDP/8 BOOTSTRAP LOADER--

### HISTORY AND GENERAL DESCRIPTION

The PDP/8 bootstrap loader was designed to do away with two very messy and time consuming features of the PDP/8.

The PDP/8 rim loader formerly had to be toggled in by hand, using the accumulator switches. This consisted of toggling in 16 instructions and depositing them in core memory. This loader is necessary to read paper tape.

The PDP/8 tape loader (20 instructions) was formerly read in via the teletype 10 CPS reader. The rim loader must have been present in order to activate the reader. The tape loader is necessary in order to use the Dectapes.

The bootstrap loader allows one to select either the rim or the tape loader option via a switch. The starting address of the selected bootstrap -1 must be set into the acc. switches and loaded with the load address key. The acc. switches are then cleared to all o's and the loader pushbutton depressed. The selected loader is automatically loaded into the PDP/8 memory. The teletype reader or the Dectapes are then ready to use.

The accumulator entry is made to the unused side of the accumulator switches. The set line is the deposit switch.

# Logic Description

The loader uses a gated clock for timing and a flip-flop register for decoding. The decoder register length is selected by the

bootstrap selector switch. The selector switch also gates the outputs of two diode matrix boards to the accumulator. Either one or the other of the two matrix boards is connected to the accumulator entry.

When the pushbutton is depressed, the clock is enabled and counts the decoder register to output the first word into the accumulator. The clock output is also used to set the deposit switch entry on the PDP/8. At clock frequency, the decoder outputs consecutively gate words from the selected matrix to the accumulator entry and the deposit line is switched. At the proper count for the selected matrix, the clock is disabled and further action is inhibited until the pushbutton is released and depressed again.

Setting the starting address to -1, when loading the loader, is necessary to insure the output of the matrix in a static condition is all o's. This will not interfere with the normal use of the accumulator switches.

### ILLIAC III INTERFACE

The interface from the PDP/8 to Illiac III is an accumulator interface. It has the capability of transferring information to and from the PDP/8 accumulator. The interface has an entry to the PDP/8 program skip bus and several IOT instructions to control the transfer. There are two control flops to control the status of the interface at the PDP/8 END, device ready, and data ready.

#### IOT List

- 6731 SKIP ON DEVICE READY

- 6732 CLEAR DEVICE READY

- 6734 CLEAR DATA RDY

- 6741 SKIP ON DATA RDY

- 6742 GATE ACCUMULATOR, SENT TO ILLIAC 3 AS DATA ACCEPTED 6744 - SENT TO ILLIAC 3 AS CONTROL

6751 6752 SENT TO ILLIAC 3 AS CONTROL 6754

# 2701 PARALLEL DATA ADAPTER\*

In order to improve the communications capability to the 360 computers in the Department, a better hardware link was required. The IBM 2701 parallel data adapter was chosen for interface purposes for at least the following reasons.

1. The 2701 allows the PDP/8 to be reasonably well isolated from the 360 channels. Thus, less chance of a system interference.

2. The parallel data adapter is a much simpler control that operates in a parallel-by-word (16 bits)-fashion over a demand-response interface.

3. This type of interface had been done before for a PDP/7 so there was some familiarity with its design.

The general operating characteristics of the PDP/8-2701 PDA interface is such as to allow either computer (360 or PDP/8) to initiate a block transfer. The 16 bit word that is transferred to the 360 is broken into two bytes of 8 bits each for 360 channel transfers. The 16 bit word as it arrives at the PDP/8 is broken into two 6 bit characters. The other four bits are not used.

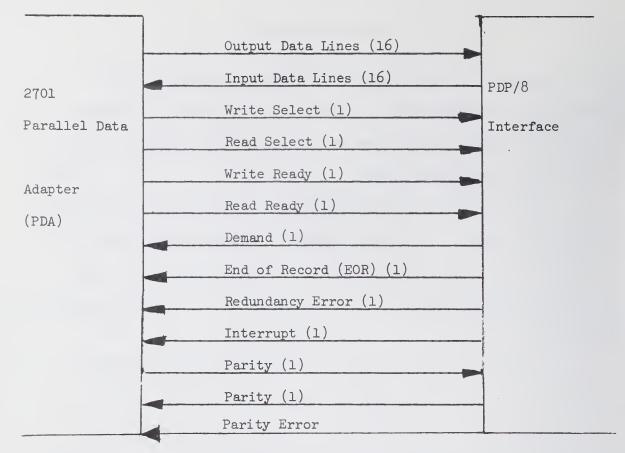

The hardware requirement for this interface was to construct a controller that would exchange information with the BDP/8 data break facility on one side and the 2701 PDA on the other. The data break requirements are reasonably simple to satisfy. The 2701 PDA interface requirements are given below.

\* See Report No. 372 for more detail.

- OUTPUT DATA LINES. From the PDA to the interface buffer register. While the word is held in the buffer register, parity is generated in the interface and compared with PDA parity.

- INPUT DATA LINES. From the interface buffer register to the PDA. Parity is generated in the interface and sent to the PDA.

- WRITE SELECT. From the PDA to the interface to signal a write operation from the 2701. This line also generates an interrupt to the PDP/8 if the write enable flop is set.

- READ SELECT. From the PDA to the interface to signal a read operation from the 2701. This line also generates an interrupt to the PDP/8 if the read enable flop is set.

- WRITE READY. From the PDA to the interface. This line notifies the interface of a data word on the bus. The data is valid and settled before the line is raised.

- READ READY. From the PDA to the interface. This line notifies the interface it is available and ready to accept a word from the bus.

DEMAND.

To the PDA from interface.

WRITE COMMAND. Signifies the interface has accepted the word on the bus.

READ COMMAND. Signifies the data on the bus is valid. Read data must be valid for the duration of the demand signal.

- REDUNDANCY ERROR. (Interface Parity Error). Interface to PDA. Indicates the interface has detected a parity error on a write operation.

- END OF RECORD (EOR). Interface to PDA. This line signifies the interface has completed the operation and will not generate or accept any more data. This line also causes the PDA to present device end and channel end status to the 360 channel.

- INTERRUPT. Interface to PDA. Signals the PDA to interrupt the CPU through the channel.

- PARITY. PDA to interface. Parity is sent simultaneously with the data bus. The interface gates the data bus into the buffer register, and calculates parity to be compared with the PDA parity.

- PARITY-INTERFACE TO PDA. The interface buffer register is loaded from the P.D.P.8 and parity is calculated from the register contents. The data and parity is sent simultaneously to the PDA.

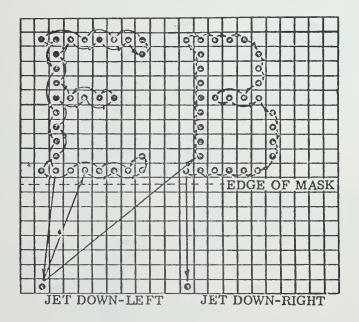

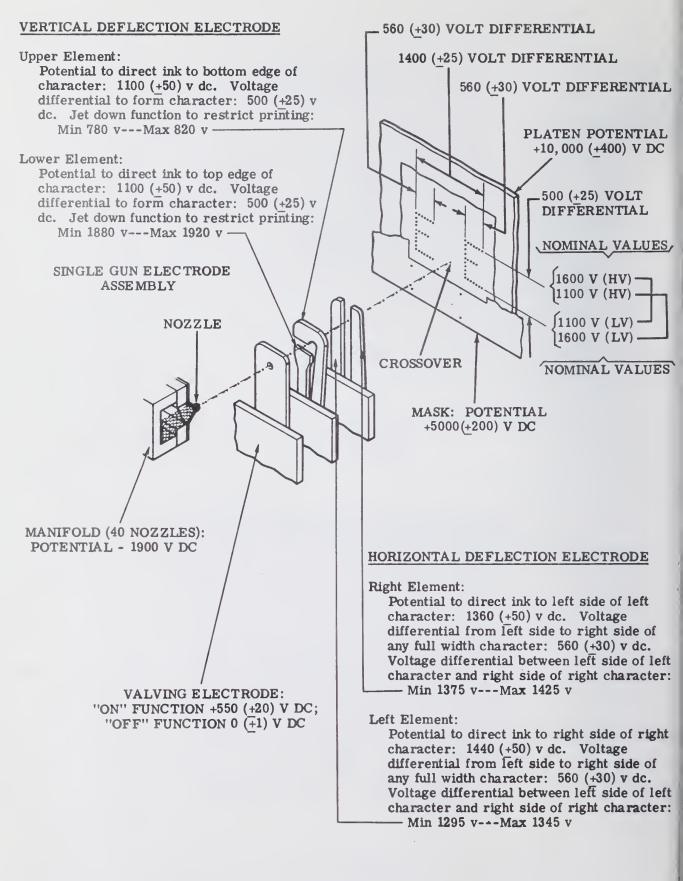

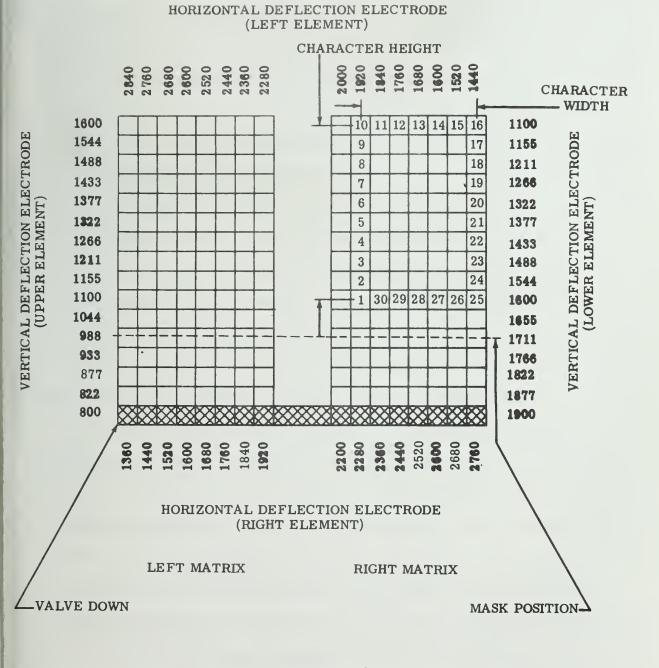

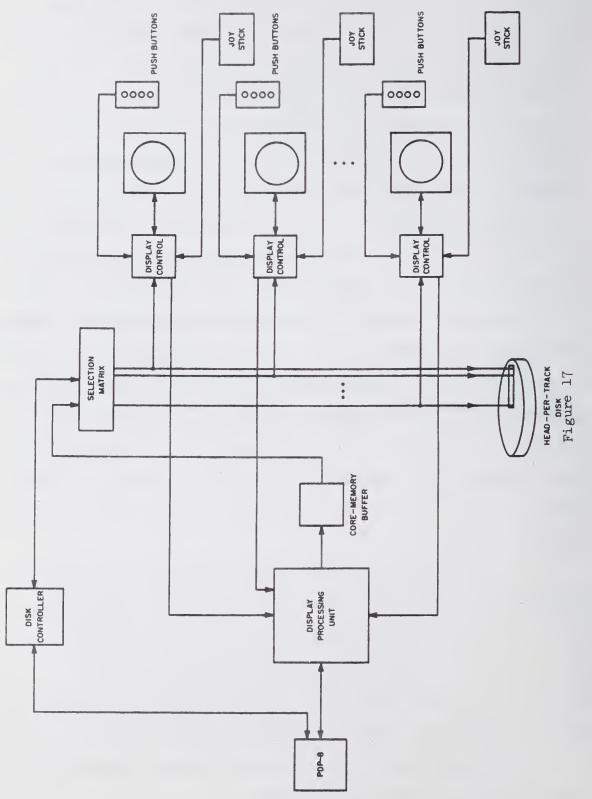

- PARITY ERROR The 2701 PDA signals the PDP/8 when an error is detected when checking parity on a read operation.